- 您现在的位置:买卖IC网 > Sheet目录324 > EK-V6-ML631-G-J (Xilinx Inc)VIRTEX-6 HXT FPGA ML631 EVAL KIT

Virtex-6 FPGA Data Sheet: DC and Switching Characteristics

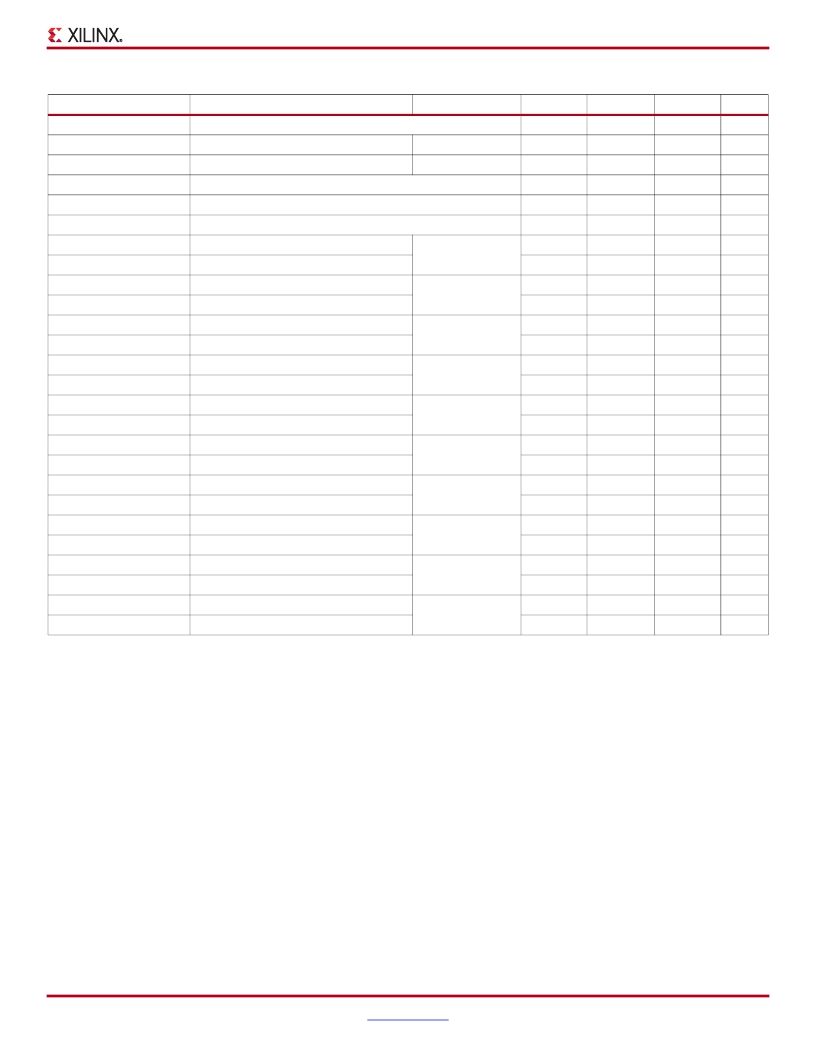

Table 23: GTX Transceiver Transmitter Switching Characteristics

F GTXTX

Symbol

Description

Serial data rate range

Condition

Min

0.480

Typ

–

Max

F GTXMAX

Units

Gb/s

T RTX

T FTX

T LLSKEW

TX Rise time

TX Fall time

TX lane-to-lane

skew (1)

20%–80%

80%–20%

–

–

–

120

120

–

–

–

350

ps

ps

ps

V TXOOBVDPP

T TXOOBTRANSITION

Electrical idle amplitude

Electrical idle transition time

–

–

–

–

15

75

mV

ns

TJ 6.5

DJ 6.5

TJ 5.0

DJ 5.0

TJ 4.25

DJ 4.25

TJ 3.75

DJ 3.75

TJ 3.125

DJ 3.125

TJ 3.125L

DJ 3.125L

TJ 2.5

DJ 2.5

TJ 1.25

DJ 1.25

TJ 600

DJ 600

TJ 480

DJ 480

Total Jitter (2)(3)

Deterministic Jitter (2)(3)

Total Jitter (2)(3)

Deterministic Jitter (2)(3)

Total Jitter (2)(3)

Deterministic Jitter (2)(3)

Total Jitter (2)(3)

Deterministic Jitter (2)(3)

Total Jitter (2)(3)

Deterministic Jitter (2)(3)

Total Jitter (2)(3)

Deterministic Jitter (2)(3)

Total Jitter (2)(3)

Deterministic Jitter (2)(3)

Total Jitter (2)(3)

Deterministic Jitter (2)(3)

Total Jitter (2)(3)

Deterministic Jitter (2)(3)

Total Jitter (2)(3)

Deterministic Jitter (2)(3)

6.5 Gb/s

5.0 Gb/s

4.25 Gb/s

3.75 Gb/s

3.125 Gb/s

3.125 Gb/s (4)

2.5 Gb/s (5)

1.25 Gb/s (6)

600 Mb/s

480 Mb/s

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

0.33

0.17

0.33

0.15

0.33

0.14

0.34

0.16

0.2

0.1

0.35

0.16

0.20

0.08

0.15

0.06

0.1

0.03

0.1

0.03

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

Notes:

1.

2.

3.

4.

5.

6.

Using same REFCLK input with TXENPMAPHASEALIGN enabled for up to 12 consecutive transmitters (three fully populated GTX Quads).

Using PLL_DIVSEL_FB = 2, 20-bit internal data width. These values are NOT intended for protocol specific compliance determinations.

All jitter values are based on a bit-error ratio of 1e -12 .

PLL frequency at 1.5625 GHz and OUTDIV = 1.

PLL frequency at 2.5 GHz and OUTDIV = 2.

PLL frequency at 2.5 GHz and OUTDIV = 4.

DS152 (v3.6) March 18, 2014

Product Specification

15

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EK-V7-VC707-CES-G

VIRTEX-7 VC707 EVAL KIT

EK-Z7-ZC702-CES-G

ZYNQ-7000 EPP ZC702 EVAL KIT

EL1848IYZ-T7

IC LED DRIVR WHITE BCKLGT 8-MSOP

EL7156CSZ

IC DRIVER PIN 40MHZ 3STATE 8SOIC

EL7158ISZ

IC DVR PIN 40MHZ 3STATE 8-SOIC

EL7222CSZ

IC DVR HS DUAL MOSFET 8-SOIC

EL7242CSZ

IC DVR HS DUAL MOSFET 8-SOIC

EL7243CMZ-T13

IC CCD DRIVER DUAL HS 20-SOIC

相关代理商/技术参数

EK-V7-VC707-CES-G

功能描述:VIRTEX-7 VC707 EVAL KIT RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-7 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

EK-V7-VC707-CES-G-J

功能描述:VIRTEX-7 VC707 EVAL KIT JAPAN RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-7 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

EK-V7-VC707-G

制造商:Xilinx 功能描述:VIRTEX-7 FPGA VC707 EVALUATION KIT - Boxed Product (Development Kits) 制造商:Xilinx 功能描述:KIT EVAL VIRTEX7 VC707 制造商:Xilinx 功能描述:VIRTEX-7 VC707 FPGA EVAL KIT

EK-V7-VC707-G-J

制造商:Xilinx 功能描述:KIT EVAL VIRTEX7 VC707 JAPAN

EKWF111

功能描述:WiFi/802.11开发工具 WF111 SDIO Eval kit

RoHS:否 制造商:Roving Networks 产品:Evaluation Boards 工具用于评估:RN-171 支持协议:802.11 b/g 频率:2.4 GHz 接口类型:UART 工作电源电压:2 V to 16 V

EKWT11-A

功能描述:蓝牙/802.15.1 开发工具 EKWT11-A

RoHS:否 制造商:Panasonic Electronic Components 产品:Bluetooth Evaluation Kit 工具用于评估:PAN1721 频率:2.4 GHz 接口类型:I2C 工作电源电压:2 V to 3.6 V

EKWT11-E

功能描述:蓝牙/802.15.1 开发工具 EKWT11-E

RoHS:否 制造商:Panasonic Electronic Components 产品:Bluetooth Evaluation Kit 工具用于评估:PAN1721 频率:2.4 GHz 接口类型:I2C 工作电源电压:2 V to 3.6 V

EKWT11i-A

功能描述:蓝牙/802.15.1 开发工具 WT11i A Eval Kit

RoHS:否 制造商:Panasonic Electronic Components 产品:Bluetooth Evaluation Kit 工具用于评估:PAN1721 频率:2.4 GHz 接口类型:I2C 工作电源电压:2 V to 3.6 V